# Ngspice User's Manual Version 40 (ngspice release version)

Holger Vogt, Giles Atkinson, Paolo Nenzi, Dietmar Warning April 1st, 2023

## Locations

The project and download pages of ngspice may be found at

Ngspice home page http://ngspice.sourceforge.net/

Project page at SourceForge http://sourceforge.net/projects/ngspice/

Download page at SourceForge https://sourceforge.net/projects/ngspice/files/ng-spice-rework/

Git source download https://sourceforge.net/p/ngspice/ngspice/ci/master/tree/

## Status

This manual is a work in progress. Some to-dos are listed in Chapt. 24.3. More is surely needed. You are invited to report bugs, missing items, wrongly described items, bad English style, etc.

#### How to use this Manual

The manual is a "work in progress." It may accompany a specific ngspice release, e.g. ngspice-35 as manual version 35. If its name contains 'Version xxplus', it describes the actual code status, found at the date of issue in the Git Source Code Management (SCM) tool. This manual is intended to provide a complete description of ngspice's functionality, features, commands, and procedures. This manual is not a book about learning SPICE usage, however the novice user may find some hints how to start using ngspice. Chapter 21.1 gives a short introduction how to set up and simulate a small circuit. Chapter 32 is about compiling and installing ngspice from a tarball or the actual Git source code, which you may find on the ngspice web pages. If you are running a specific Linux distribution, you may check if it provides ngspice as part of the package. Some are listed here.

## License

This document is covered by the Creative Commons Attribution Share-Alike (CC-BY-SA) v4.0..

Part of chapters 12 and 25-27 are in the public domain.

Chapter 30 is covered by New BSD (chapt. 33.3.2).

# Part I Ngspice User's Manual

# Contents

| Ι | Ng   | gspice | e User's Manual                              | 3  |

|---|------|--------|----------------------------------------------|----|

| 1 | Intr | oduct  | ion                                          | 35 |

|   | 1.1  | Simula | ation Algorithms                             | 36 |

|   |      | 1.1.1  | Analog Simulation                            | 36 |

|   |      | 1.1.2  | Device Models for Analog Simulation          | 36 |

|   |      | 1.1.3  | Digital Simulation                           | 37 |

|   |      | 1.1.4  | Mixed-Signal Simulation                      | 37 |

|   |      | 1.1.5  | Mixed-Level Simulation (Electronic and TCAD) | 38 |

|   | 1.2  | Suppo  | orted Analyses                               | 39 |

|   |      | 1.2.1  | DC Analysis                                  | 39 |

|   |      | 1.2.2  | AC Small-Signal Analysis                     | 40 |

|   |      | 1.2.3  | Transient Analysis                           | 40 |

|   |      | 1.2.4  | Pole-Zero Analysis                           | 40 |

|   |      | 1.2.5  | Small-Signal Distortion Analysis             | 41 |

|   |      | 1.2.6  | Sensitivity Analysis                         | 41 |

|   |      | 1.2.7  | Noise Analysis                               | 42 |

|   |      | 1.2.8  | Periodic Steady State Analysis               | 42 |

|   | 1.3  | Analy  | rsis at Different Temperatures               | 42 |

|   |      | 1.3.1  | Introduction                                 | 42 |

|   |      | 1.3.2  | Controlling the temperature                  | 44 |

|   | 1.4  | Conve  | ergence                                      | 45 |

|   |      | 1.4.1  | Voltage convergence criterion                | 45 |

|   |      | 1.4.2  | Current convergence criterion                | 46 |

|   |      | 1.4.3  | Convergence failure                          | 46 |

| 2 | Circ | cuit Description 4                                                | 7  |

|---|------|-------------------------------------------------------------------|----|

|   | 2.1  | General Structure and Conventions                                 | 17 |

|   |      | 2.1.1 Input file structure                                        | 17 |

|   |      | 2.1.2 Syntax check                                                | 17 |

|   |      | 2.1.3 Circuit elements (device instances)                         | 18 |

|   |      | 2.1.4 Some naming conventions                                     | 19 |

|   |      | 2.1.5 Topological constraints                                     | 51 |

|   | 2.2  | Dot commands                                                      | 51 |

|   | 2.3  | Basic lines                                                       | 53 |

|   |      | 2.3.1 .TITLE line                                                 | 53 |

|   |      | 2.3.2 .END Line                                                   | 53 |

|   |      | 2.3.3 Comments                                                    | 54 |

|   |      | 2.3.4 End-of-line comments                                        | 54 |

|   |      | 2.3.5 Continuation lines                                          | 54 |

|   | 2.4  | .MODEL Device Models                                              | 55 |

|   | 2.5  | .SUBCKT Subcircuits                                               | 6  |

|   |      | 2.5.1 .SUBCKT Line                                                | 67 |

|   |      | 2.5.2 .ENDS Line                                                  | 67 |

|   |      | 2.5.3 Subcircuit Calls                                            | 8  |

|   | 2.6  | .GLOBAL                                                           | 8  |

|   | 2.7  | .INCLUDE                                                          | 8  |

|   | 2.8  | .LIB                                                              | 59 |

|   | 2.9  | .PARAM Parametric netlists                                        | 59 |

|   |      | 2.9.1 .param line                                                 | 59 |

|   |      | 2.9.2 Brace expressions in circuit elements:                      | 60 |

|   |      | 2.9.3 Subcircuit parameters                                       | 61 |

|   |      | 2.9.4 Symbol scope                                                | 52 |

|   |      | 2.9.5 Syntax of expressions                                       | 62 |

|   |      | 2.9.6 Reserved words                                              | 35 |

|   |      | 2.9.7 A word of caution on the three ngspice expression parsers 6 | 35 |

|   | 2.10 | .FUNC                                                             | 55 |

|   | 2.11 | .CSPARAM                                                          | 66 |

|   | 2.12 | .TEMP                                                             | 66 |

|   | 2.13 | .IF Condition-Controlled Netlist                                  | 57 |

|   | 2.14 | Parameters, functions, expressions, and command scripts 6         | 69 |

|   |      |                                                                   | 59 |

|   |      | 2.14.2 Nonlinear sources                                          | 59 |

|   |      |                                                                   | 59 |

| 3 | Circ | cuit Ele | ements and Models                                           | <b>7</b> 1 |

|---|------|----------|-------------------------------------------------------------|------------|

|   | 3.1  | About    | netlists, device instances, models and model parameters     | 71         |

|   | 3.2  | Genera   | al options                                                  | 73         |

|   |      | 3.2.1    | Paralleling devices with multiplier m                       | 73         |

|   |      | 3.2.2    | Instance and model parameters                               | 75         |

|   |      | 3.2.3    | Model binning                                               | 75         |

|   |      | 3.2.4    | Initial conditions                                          | 75         |

|   | 3.3  | Elemen   | ntary Devices                                               | 76         |

|   |      | 3.3.1    | Resistors                                                   | 76         |

|   |      | 3.3.2    | Semiconductor Resistors                                     | 78         |

|   |      | 3.3.3    | Semiconductor Resistor Model (R)                            | 78         |

|   |      | 3.3.4    | Resistors, dependent on expressions (behavioral resistor)   | 80         |

|   |      | 3.3.5    | Resistor with nonlinear r2_cmc model                        | 80         |

|   |      | 3.3.6    | Capacitors                                                  | 81         |

|   |      | 3.3.7    | Semiconductor Capacitors                                    | 82         |

|   |      | 3.3.8    | Semiconductor Capacitor Model (C)                           | 82         |

|   |      | 3.3.9    | Capacitors, dependent on expressions (behavioral capacitor) | 84         |

|   |      | 3.3.10   | Inductors                                                   | 85         |

|   |      | 3.3.11   | Inductor model                                              | 86         |

|   |      | 3.3.12   | Coupled (Mutual) Inductors                                  | 87         |

|   |      | 3.3.13   | Inductors, dependent on expressions (behavioral inductor)   | 88         |

|   |      | 3.3.14   | Capacitor or inductor with initial conditions               | 89         |

|   |      | 3.3.15   | Switches                                                    | 90         |

|   |      | 3.3.16   | Switch Model (SW/CSW)                                       | 91         |

| 4 | Vol  | tage ar  | nd Current Sources                                          | 93         |

|   | 4.1  | Indepe   | endent Sources for Voltage or Current                       |            |

|   |      | 4.1.1    | Pulse                                                       | 94         |

|   |      | 4.1.2    | Sinusoidal                                                  | 95         |

|   |      | 4.1.3    | Exponential                                                 | 96         |

|   |      | 4.1.4    | Piece-Wise Linear                                           | 96         |

|   |      | 4.1.5    | Single-Frequency FM                                         | 97         |

|   |      | 4.1.6    | Amplitude modulated source (AM)                             | 97         |

|   |      | 4.1.7    | Transient noise source                                      | 98         |

|   |      | 4.1.8    | Random voltage source                                       | 99         |

|   |     | 4.1.9    | External voltage or current input                          | . 100 |

|---|-----|----------|------------------------------------------------------------|-------|

|   |     | 4.1.10   | Arbitrary Phase Sources                                    | . 100 |

|   |     | 4.1.11   | RF Port                                                    | . 100 |

|   | 4.2 | Linear   | Dependent Sources                                          | . 101 |

|   |     | 4.2.1    | Gxxxx: Linear Voltage-Controlled Current Sources (VCCS) $$ | . 101 |

|   |     | 4.2.2    | Exxxx: Linear Voltage-Controlled Voltage Sources (VCVS)    | . 101 |

|   |     | 4.2.3    | Fxxxx: Linear Current-Controlled Current Sources (CCCS) $$ | . 102 |

|   |     | 4.2.4    | Hxxxx: Linear Current-Controlled Voltage Sources (CCVS) $$ | . 102 |

|   |     | 4.2.5    | Polynomial Source Compatibility                            | . 102 |

| 5 | Nor | ı-lineaı | r Dependent Sources (Behavioral Sources)                   | 105   |

|   | 5.1 | Bxxxx    | :: Nonlinear dependent source (ASRC)                       | . 105 |

|   |     | 5.1.1    | Syntax and usage                                           | . 105 |

|   |     | 5.1.2    | Special B-Source Variables time, temper, hertz             | . 109 |

|   |     | 5.1.3    | par('expression')                                          | . 109 |

|   |     | 5.1.4    | Piecewise Linear Function: pwl                             | . 109 |

|   | 5.2 | Exxxx    | :: non-linear voltage source                               | . 112 |

|   |     | 5.2.1    | VOL                                                        | . 112 |

|   |     | 5.2.2    | VALUE                                                      | . 112 |

|   |     | 5.2.3    | TABLE                                                      | . 112 |

|   |     | 5.2.4    | POLY                                                       | . 113 |

|   |     | 5.2.5    | LAPLACE                                                    | . 113 |

|   | 5.3 | Gxxxx    | c: non-linear current source                               | . 114 |

|   |     | 5.3.1    | CUR                                                        | . 114 |

|   |     | 5.3.2    | VALUE                                                      | . 114 |

|   |     | 5.3.3    | TABLE                                                      | . 115 |

|   |     | 5.3.4    | POLY                                                       | . 115 |

|   |     | 5.3.5    | LAPLACE                                                    | . 115 |

|   |     | 5.3.6    | Example                                                    | . 115 |

|   | 5.4 | Debug    | ging a behavioral source                                   | . 116 |

|   | 5.5 | POLY     | Sources                                                    | . 117 |

|   |     | 5.5.1    | E voltage source, G current source                         | . 118 |

|   |     | 5.5.2    | F voltage source, H current source                         | . 118 |

| 6  | Tra           | nsmiss         | ion Lines                                            | 121     |

|----|---------------|----------------|------------------------------------------------------|---------|

|    | 6.1           | Lossles        | ss Transmission Lines                                | <br>121 |

|    | 6.2           | Lossy          | Transmission Lines                                   | <br>122 |

|    |               | 6.2.1          | Lossy Transmission Line Model (LTRA)                 | <br>122 |

|    | 6.3           | Unifor         | rm Distributed RC Lines                              | <br>124 |

|    |               | 6.3.1          | Uniform Distributed RC Model (URC)                   | <br>124 |

|    | 6.4           | KSPIC          | CE Lossy Transmission Lines                          | <br>125 |

|    |               | 6.4.1          | Single Lossy Transmission Line (TXL)                 | <br>126 |

|    |               | 6.4.2          | Coupled Multiconductor Line (CPL)                    | <br>126 |

| 7  | Dio           | $\mathbf{des}$ |                                                      | 129     |

|    | 7.1           | Juncti         | ion Diodes                                           | <br>129 |

|    | 7.2           | Diode          | Model (D)                                            | <br>130 |

|    | 7.3           | Diode          | Equations                                            | <br>133 |

| 8  | вјт           | Γ              |                                                      | 139     |

|    | 8.1           | Bipola         | ar Junction Transistors (BJTs)                       | <br>139 |

|    | 8.2           | BJT N          | Models (NPN/PNP)                                     | <br>139 |

|    |               | 8.2.1          | Gummel-Poon Models                                   | <br>140 |

|    |               | 8.2.2          | VBIC Model                                           | <br>145 |

|    |               | 8.2.3          | MEXTRAM Model                                        | <br>147 |

|    |               | 8.2.4          | HICUM level 2 Model                                  | <br>148 |

|    |               | 8.2.5          | HICUM level 0 Model                                  | <br>149 |

| 9  | JFE           | ${f cTs}$      |                                                      | 151     |

|    | 9.1           | Juncti         | ion Field-Effect Transistors (JFETs)                 | <br>151 |

|    | 9.2           | JFET           | Models (NJF/PJF)                                     | <br>151 |

|    |               | 9.2.1          | Basic model statement                                | <br>151 |

|    |               | 9.2.2          | JFET level 1 model with Parker Skellern modification | <br>151 |

|    |               | 9.2.3          | JFET level 2 Parker Skellern model                   | <br>154 |

| 10 | $\mathbf{ME}$ | SFETs          | 3                                                    | 157     |

|    | 10.1          | MESF           | $ m ^{ m ETs}$                                       | <br>157 |

|    | 10.2          | MESF           | ET Models (NMF/PMF)                                  | <br>157 |

|    |               |                | Basic model statements                               |         |

|    |               | 10.2.2         | Model by Statz e.a                                   | <br>157 |

|    |               | 10.2.3         | Model by Ytterdal e.a                                | <br>158 |

|    |               | 10.2.4         | hfet1                                                | <br>158 |

|    |               | 10.2.5         | hfet2                                                | <br>159 |

| 11 N | IOSFETs                                                       | 161         |

|------|---------------------------------------------------------------|-------------|

| 13   | 1.1 MOSFET devices                                            | 161         |

| 1:   | 1.2 MOSFET models (NMOS/PMOS)                                 | 162         |

|      | 11.2.1 MOS Level 1                                            | 164         |

|      | 11.2.2 MOS Level 2                                            | 164         |

|      | 11.2.3 MOS Level 3                                            | 164         |

|      | 11.2.4 MOS Level 6                                            | 164         |

|      | 11.2.5 Notes on Level 1-6 models                              | 164         |

|      | 11.2.6 MOS Level 9                                            | 167         |

|      | 11.2.7 BSIM Models                                            | 167         |

|      | 11.2.8 BSIM1 model (level 4)                                  | 168         |

|      | 11.2.9 BSIM2 model (level 5)                                  | 170         |

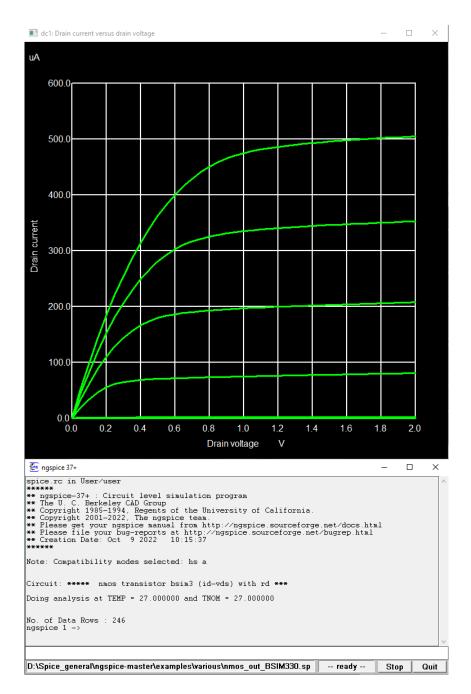

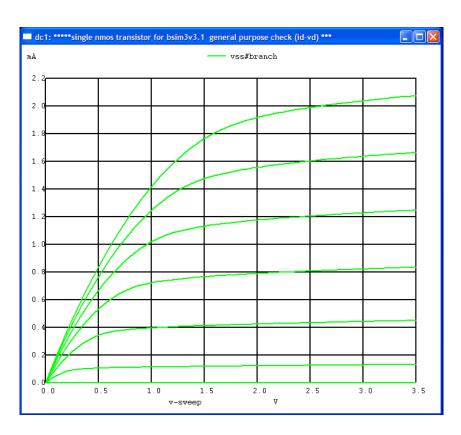

|      | $11.2.10\mathrm{BSIM3}$ model (levels $8,49$ )                | 170         |

|      | 11.2.11 BSIM4 model (levels 14, 54)                           | 171         |

|      | 11.2.12 EKV2.6 Model                                          | 171         |

|      | 11.2.13 PSP Model                                             | 172         |

|      | $11.2.14\mathrm{BSIMSOI}$ models (levels 10, 58, 55, 56, 57)  | 172         |

|      | $11.2.15\mathrm{SOI3}$ model (level 60)                       | 173         |

|      | $11.2.16\mathrm{HiSIM}$ models of the University of Hiroshima | 173         |

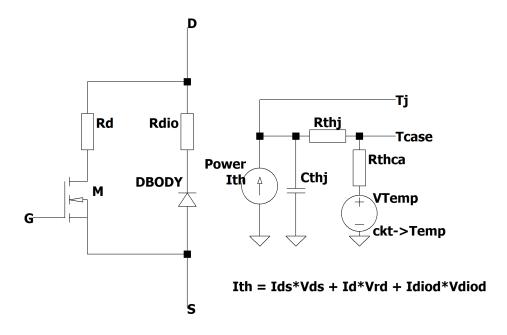

| 13   | 1.3 Power MOSFET model (VDMOS)                                | 173         |

| 12 N | fixed-Mode and Behavioral Modeling with XSPICE                | <b>17</b> 9 |

| 15   | 2.1 Code Model Element & .MODEL Cards                         | 179         |

|      | 12.1.1 Syntax                                                 | 179         |

|      | 12.1.2 Examples                                               | 183         |

|      | 12.1.3 Search path for file input                             | 184         |

|      | 12.1.4 Code model location and assessment                     | 184         |

| 12   | 2.2 Analog Models                                             | 185         |

|      | 12.2.1 Gain                                                   | 185         |

|      | 12.2.2 Summer                                                 | 186         |

|      | 12.2.3 Multiplier                                             | 187         |

|      | 12.2.4 Divider                                                |             |

|      | 12.2.5 Limiter                                                | 190         |

|      | 12.2.6 Controlled Limiter                                     |             |

|      | 12.2.7 PWL Controlled Source                                  | 193         |

|      | 12.2.8 PWL Time Controlled Source with optional edge smoothing .    |  | 195 |

|------|---------------------------------------------------------------------|--|-----|

|      | 12.2.9 Filesource (PWL sourced from file)                           |  | 197 |

|      | $12.2.10\mathrm{multi\_input\_pwl}$ block                           |  | 199 |

|      | 12.2.11 Analog Switch                                               |  | 200 |

|      | 12.2.12 Alternative Analog Switch                                   |  | 201 |

|      | 12.2.13 Zener Diode                                                 |  | 202 |

|      | 12.2.14 Current Limiter                                             |  | 204 |

|      | 12.2.15 Hysteresis Block                                            |  | 206 |

|      | 12.2.16 Differentiator                                              |  | 208 |

|      | 12.2.17 Integrator                                                  |  | 209 |

|      | 12.2.18 S-Domain Transfer Function                                  |  | 211 |

|      | 12.2.19 Slew Rate Block                                             |  | 214 |

|      | 12.2.20 Inductive Coupling                                          |  | 215 |

|      | 12.2.21 Magnetic Core                                               |  | 216 |

|      | 12.2.22 Controlled Sine Wave Oscillator                             |  | 219 |

|      | 12.2.23 Controlled Triangle Wave Oscillator                         |  | 220 |

|      | 12.2.24 Controlled Square Wave Oscillator                           |  | 222 |

|      | 12.2.25 Controlled One-Shot                                         |  | 223 |

|      | 12.2.26 Capacitance Meter                                           |  | 226 |

|      | 12.2.27 Inductance Meter                                            |  | 226 |

|      | 12.2.28 Memristor                                                   |  | 227 |

|      | 12.2.29 2D table model                                              |  | 228 |

|      | 12.2.30 3D table model                                              |  | 230 |

|      | 12.2.31 Simple Diode Model                                          |  | 232 |

|      | 12.2.32 Analog delay                                                |  | 234 |

|      | 12.2.33 Potentiometer                                               |  | 235 |

| 12.3 | Hybrid Models                                                       |  | 236 |

|      | 12.3.1 Digital-to-Analog Node Bridge                                |  | 236 |

|      | 12.3.2 Analog-to-Digital Node Bridge                                |  | 238 |

|      | 12.3.3 Bidirectional Analog/Digital Node Bridge                     |  | 239 |

|      | 12.3.4 Controlled Digital Oscillator                                |  | 243 |

|      | 12.3.5 Node bridge from digital to real with enable $\dots \dots$ . |  | 244 |

|      | 12.3.6 A Z**-1 block working on real data                           |  | 244 |

|      | 12.3.7 A gain block for event-driven real data                      |  | 245 |

|      | 12.3.8 Node bridge from real to analog voltage                      |  | 246 |

|      |                                                                     |  |     |

|      | 12.3.9 Controlled PWM Oscillator                  | 246 |

|------|---------------------------------------------------|-----|

| 12.4 | Digital Models                                    | 248 |

|      | 12.4.1 Buffer                                     | 250 |

|      | 12.4.2 Inverter                                   | 250 |

|      | 12.4.3 And                                        | 251 |

|      | 12.4.4 Nand                                       | 252 |

|      | 12.4.5 Or                                         | 252 |

|      | 12.4.6 Nor                                        | 253 |

|      | 12.4.7 Xor                                        | 253 |

|      | 12.4.8 Xnor                                       | 254 |

|      | 12.4.9 Tristate                                   | 254 |

|      | 12.4.10 Pullup                                    | 256 |

|      | 12.4.11 Pulldown                                  | 256 |

|      | 12.4.12 D Flip Flop                               | 257 |

|      | 12.4.13 JK Flip Flop                              | 259 |

|      | 12.4.14 Toggle Flip Flop                          | 261 |

|      | 12.4.15 Set-Reset Flip Flop                       | 263 |

|      | 12.4.16 D Latch                                   | 265 |

|      | 12.4.17 Set-Reset Latch                           | 267 |

|      | 12.4.18 State Machine                             | 270 |

|      | 12.4.19 Frequency Divider                         | 273 |

|      | 12.4.20 RAM                                       | 274 |

|      | 12.4.21 Digital Source                            | 276 |

|      | 12.4.22 LUT                                       | 278 |

|      | 12.4.23 General LUT                               | 278 |

| 12.5 | Predefined Node Types for event driven simulation | 280 |

|      | 12.5.1 Digital Node Type                          | 280 |

|      | 12.5.2 Real Node Type                             | 280 |

|      | 12.5.3 Int Node Type                              | 281 |

|      | 12.5.4 (Digital) Input/Output                     | 281 |

| 12.6 | Automatic insertion of bridging devices           | 281 |

| <b>13</b> | Veri | ilog-A Compact Device Models                              | 285 |

|-----------|------|-----------------------------------------------------------|-----|

|           | 13.1 | Introduction                                              | 285 |

|           | 13.2 | OSDI/OpenVAF                                              | 285 |

|           | 13.3 | How to create and apply OpenVAF models                    | 285 |

|           |      | 13.3.1 Preparing for simulation                           | 285 |

|           |      | 13.3.2 OSDI/OpenVAF examples distributed with ngspice     | 288 |

|           | 13.4 | ADMS (deprecated)                                         | 289 |

|           |      | 13.4.1 Introduction                                       | 289 |

|           |      | 13.4.2 How to integrate a Verilog-A model into ngspice    | 289 |

| 14        | Digi | ital Device Models                                        | 291 |

|           | 14.1 | U devices (basic digital building blocks)                 | 291 |

|           |      | 14.1.1 General format                                     | 292 |

|           |      | 14.1.2 List of devices available in ngspice (basic types) | 292 |

|           |      | 14.1.3 URC transmission line versus U devices             | 293 |

|           | 14.2 | Support for standard digital devices                      | 293 |

| <b>15</b> | Ana  | lyses and Output Control (batch mode)                     | 295 |

|           | 15.1 | Simulator Variables (.options)                            | 295 |

|           |      | 15.1.1 General Options                                    | 296 |

|           |      | 15.1.2 OP and DC Solution Options                         | 297 |

|           |      | 15.1.3 AC Solution Options                                | 299 |

|           |      | 15.1.4 Transient Analysis Options                         | 299 |

|           |      | 15.1.5 ELEMENT Specific options                           | 300 |

|           |      | 15.1.6 Transmission Lines Specific Options                | 301 |

|           |      | 15.1.7 Precedence of option and .options commands         | 301 |

|           | 15.2 | Initial Conditions                                        | 301 |

|           |      | 15.2.1 .NODESET: Specify Initial Node Voltage Guesses     | 301 |

|           |      | 15.2.2 .IC: Set Initial Conditions                        | 302 |

|           | 15.3 | Analyses                                                  | 303 |

|           |      | 15.3.1 .AC: Small-Signal AC Analysis                      | 303 |

|           |      | 15.3.2 .DC: DC Transfer Function                          | 304 |

|           |      | 15.3.3 .DISTO: Distortion Analysis                        | 304 |

|           |      | 15.3.4 .NOISE: Noise Analysis                             | 306 |

|           |      | 15.3.5 .OP: Operating Point Analysis                      | 307 |

|           |      | 15.3.6 .PZ: Pole-Zero Analysis                            | 309 |

|      | 15.3.7 .SENS: DC or Small-Signal AC Sensitivity Analysis                                                             | . 309 |

|------|----------------------------------------------------------------------------------------------------------------------|-------|

|      | 15.3.8 .SP S-Parameter Analysis                                                                                      | . 310 |

|      | 15.3.9 .TF: Transfer Function Analysis                                                                               | . 311 |

|      | 15.3.10.TRAN: Transient Analysis                                                                                     | . 311 |

|      | 15.3.11 Transient noise analysis (at low frequency)                                                                  | . 312 |

|      | 15.3.12.PSS: Periodic Steady State Analysis                                                                          | . 315 |

| 15.4 | Measurements after AC, DC and Transient Analysis                                                                     | . 316 |

|      | 15.4.1 .meas(ure)                                                                                                    | . 316 |

|      | 15.4.2 batch versus interactive mode                                                                                 | . 316 |

|      | 15.4.3 General remarks                                                                                               | . 316 |

|      | 15.4.4 Input                                                                                                         | . 317 |

|      | 15.4.5 Trig Targ                                                                                                     | . 318 |

|      | 15.4.6 Find When                                                                                                     | . 319 |

|      | 15.4.7 AVG MIN MAX PP RMS MIN_AT MAX_AT                                                                              | . 320 |

|      | 15.4.8 Integ                                                                                                         | . 321 |

|      | 15.4.9 param                                                                                                         | . 321 |

|      | 15.4.10 par('expression')                                                                                            | . 321 |

|      | 15.4.11 Deriv                                                                                                        | . 322 |

|      | 15.4.12 More examples                                                                                                | . 322 |

| 15.5 | Safe Operating Area (SOA) warning messages                                                                           | . 323 |

|      | 15.5.1 Resistor and Capacitor SOA model parameters                                                                   | . 324 |

|      | 15.5.2 Diode SOA model parameters                                                                                    | . 324 |

|      | 15.5.3 BJT SOA model parameters                                                                                      | . 325 |

|      | 15.5.4 MOS SOA model parameters                                                                                      | . 326 |

|      | 15.5.5 VDMOS SOA model parameters                                                                                    | . 327 |

| 15.6 | Batch Output                                                                                                         | . 327 |

|      | 15.6.1 .SAVE: Name vector(s) to be saved in raw file                                                                 | . 327 |

|      | 15.6.2 .PRINT Lines                                                                                                  | . 328 |

|      | 15.6.3 .PLOT Lines                                                                                                   | . 329 |

|      | 15.6.4 .FOUR: Fourier Analysis of Transient Analysis Output                                                          | . 329 |

|      | 15.6.5 .PROBE: Save device node currents, device power dissipation, or differential voltages between arbitrary nodes | . 330 |

|      | 15.6.6 par('expression'): Algebraic expressions for output                                                           | . 334 |

|      | 15.6.7 .width                                                                                                        | . 335 |

| 15.7 | Measuring current through device terminals                                                                           | . 335 |

|      | 15.7.1 Using the .probe command                                                                                      | . 335 |

|      | 15.7.2 Adding a voltage source in series                                                                             | . 335 |

|      | 15.7.3 Using option 'savecurrents'                                                                                   | . 336 |

| 16 Starting ngspice       337         16.1 Introduction       337         16.2 Where to obtain ngspice       337         16.3 Command line options for starting ngspice       338         16.4 Starting options       340         16.4.1 Batch mode       340         16.4.2 Interactive mode       340         16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10 Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.14Compatibility       352 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16.2 Where to obtain ngspice       337         16.3 Command line options for starting ngspice       338         16.4 Starting options       340         16.4.1 Batch mode       340         16.4.2 Interactive mode       340         16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10 Ngspice on multi-core processors using OpenMP       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -p       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                 |

| 16.3 Command line options for starting ngspice       338         16.4 Starting options       340         16.4.1 Batch mode       340         16.4.2 Interactive mode       340         16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file .spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10 Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                     |

| 16.4 Starting options       340         16.4.1 Batch mode       340         16.4.2 Interactive mode       340         16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10 Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11 Server mode option -s       348         16.12 Pipe mode option -p       349         16.13 Ngspice control via input, output fifos       351                                                                                                                                                                                    |

| 16.4.1 Batch mode       340         16.4.2 Interactive mode       340         16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                          |

| 16.4.2 Interactive mode       340         16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file .spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       345         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                      |

| 16.4.3 Control mode (Interactive mode with control file or control section)       341         16.5 Standard configuration file spinit       342         16.6 User defined configuration file spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       345         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                 |

| 16.5 Standard configuration file spinit       342         16.6 User defined configuration file .spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10 Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12 Pipe mode option -p       349         16.13 Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                           |

| 16.6 User defined configuration file .spiceinit       343         16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       345         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                        |

| 16.7 Environmental variables       344         16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16.7.1 Ngspice specific variables       344         16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.7.2 Common environment variables       344         16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16.8 Memory usage       345         16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16.9 Simulation time       345         16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16.10Ngspice on multi-core processors using OpenMP       345         16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

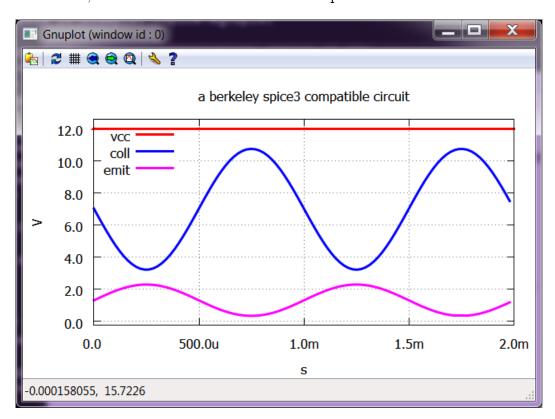

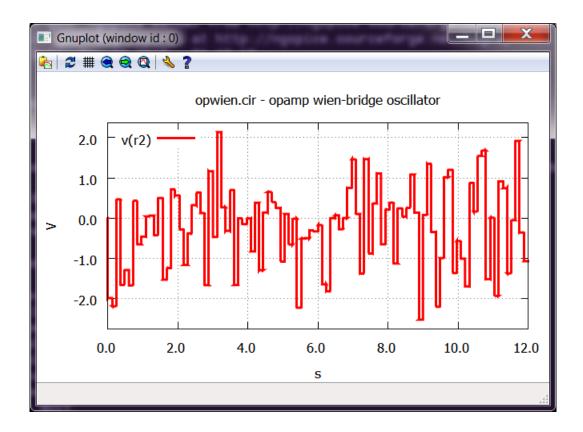

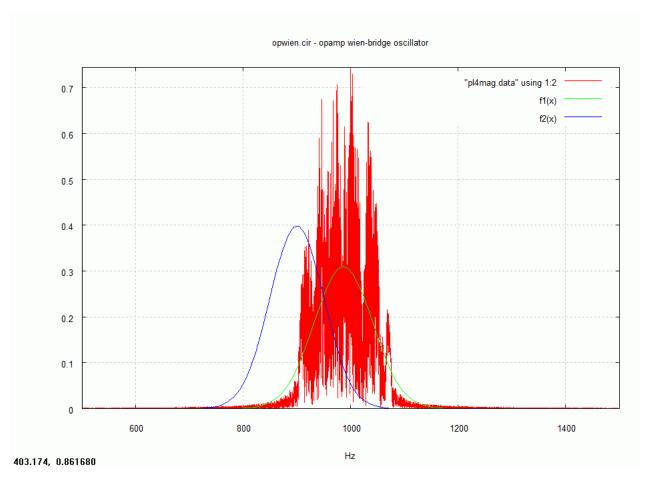

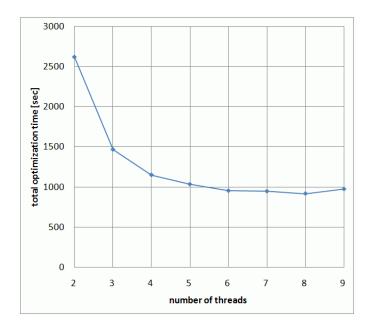

| 16.10.1 Introduction       345         16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12 Pipe mode option -p       349         16.13 Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16.10.2 Internals       346         16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11 Server mode option -s       348         16.12 Pipe mode option -p       349         16.13 Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16.10.3 Some results       346         16.10.4 Usage       347         16.10.5 Literature       348         16.11 Server mode option -s       348         16.12 Pipe mode option -p       349         16.13 Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16.10.4 Usage       347         16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16.10.5 Literature       348         16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16.11Server mode option -s       348         16.12Pipe mode option -p       349         16.13Ngspice control via input, output fifos       351                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16.12Pipe mode option -p <td< td=""></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16.13Ngspice control via input, output fifos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.14Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.14.1 Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16.14.2 Missing functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16.14.3 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.14.4 Controls and commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16.14.5 PSPICE Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16.14.6 LTSPICE Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16.14.7LTSPICE/PSPICE Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16.14.8 KiCad Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16.14.9 Spectre Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16.14.10HSPICE Compatibility mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16.1   | 15Tests                                                                     | . 359 |

|--------|-----------------------------------------------------------------------------|-------|

| 16.1   | 16Tools for debugging a circuit netlist                                     | . 360 |

|        | 16.16.1 options and initial conditions                                      | . 360 |

|        | 16.16.2 set debug                                                           | . 360 |

|        | 16.16.3 set ngdebug                                                         | . 361 |

|        | 16.16.4 miscellaneous                                                       | . 361 |

| 16.1   | 17Reporting bugs and errors                                                 | . 361 |

| 17 Int | eractive Interpreter                                                        | 363   |

| 17.1   | 1 Introduction                                                              | . 363 |

| 17.2   | 2 Expressions, Functions, and Constants                                     | . 364 |

| 17.3   | 3 Plots                                                                     | . 368 |

| 17.4   | 4 Command Interpretation                                                    | . 369 |

|        | 17.4.1 On the console                                                       | . 369 |

|        | 17.4.2 Scripts                                                              | . 369 |

|        | 17.4.3 Add-on to circuit file                                               | . 370 |

| 17.5   | 5 Commands                                                                  | . 370 |

|        | 17.5.1 Ac*: Perform an AC, small-signal frequency response analysis $\dots$ | . 370 |

|        | 17.5.2 Alias: Create an alias for a command                                 | . 371 |

|        | 17.5.3 Alter*: Change a device or model parameter                           | . 371 |

|        | 17.5.4 Altermod*: Change model parameter(s)                                 | . 373 |

|        | 17.5.5 Alterparam*: Change value of a global parameter                      | . 374 |

|        | 17.5.6 Asciiplot: Plot values using old-style character plots               | . 375 |

|        | 17.5.7 Aspice*: Asynchronous ngspice run                                    | . 375 |

|        | 17.5.8 Bug: Output URL for ngspice bug tracker                              | . 375 |

|        | 17.5.9 Cd: Change directory                                                 | . 375 |

|        | $17.5.10\mathrm{Cdump}$ : Dump the control flow to the screen               | . 376 |

|        | 17.5.11 Circbyline*: Enter a circuit line by line                           | . 376 |

|        | 17.5.12 Codemodel*: Load an XSPICE code model library                       | . 377 |

|        | 17.5.13 Compose: Compose a vector                                           | . 378 |

|        | 17.5.14 Cutout: Cut out a section of all vectors in a tran plot             | . 379 |

|        | 17.5.15 Dc*: Perform a DC-sweep analysis                                    | . 379 |

|        | 17.5.16 Define: Define a function                                           | . 379 |

|        | 17.5.17 Deftype: Define a new type for a vector or plot                     |       |

|        | 17.5.18 Delete*: Remove a trace or breakpoint                               | . 380 |

| 17.5.19 Destroy: Delete an output data set $\dots \dots \dots$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17.5.20 Devhelp: information on available devices                                                                                                              |

| 17.5.21 Diff: Compare vectors                                                                                                                                  |

| 17.5.22 Display: List known vectors and types                                                                                                                  |

| 17.5.23 Echo: Print text                                                                                                                                       |

| $17.5.24\mathrm{Edit}^*$ : Edit the current circuit                                                                                                            |